- Admin

- February 24, 2025

Case Study

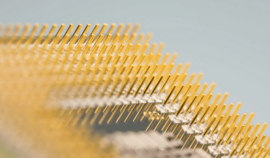

OpenOCD debug framework support over JTAG

Client

A US-based chip startup developing the first digital radar-on-chip for Automotive applications approached Ignitarium for setting up a reliable and cost-effective debug and validation infrastructure for a multi-core SoC. The expectation was to be able to proceed with basic software development activities, pre and post silicon validation, in a short period of time.

Challenges

To have a custom debug test suite to enable validation, testing and development of software modules, IPs etc. with the flexibility to tailor the JTAG based test suite to custom requirements. The costs and efforts associated with partnering with leading players like Lauterbach or Segger for a single chip startup were understood to be prohibitively high. Rapid prototyping was to be done on FPGA like most SoCs, the customer wanted the same JTAG solution to be able to be RUN and validated on FPGA before incorporating into the SoC in a very short period of time.

Solution

Ignitarium experts recommended a low cost solution by leveraging open source software, OpenOCD; thereafter the team architected and implemented the same and engineered the required changes to meet the custom requirements. Development progressed from FPGA to SoC which required to enable a debug interface on Multicore ARM architecture communicating via AXI and a high speed AHB to a low power APB bridge.

Business Impact

Ignitarium’s recommended solution of OpenOCD over JTAG empowered the customer to not only complete the testing and validation process well within the budget, but also to successfully enable various engineering teams across the globe to quickly validate the internal hardware functionality, software modules and IP Blocks.

The solution provided the flexibility to seamlessly adopt customization to the JTAG chain to validate the newly added IP blocks and feature debug.

25x cost savings vs. Standard established tools

Enables remote engineers from across the globe to get their debug data efficiently & quickly

Lower cost of each setup enables more number of setups for customer test teams to test and validate the software components