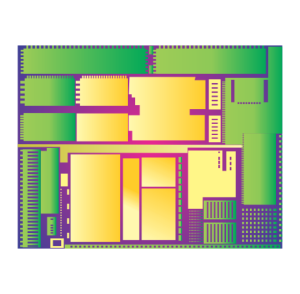

PHYSICAL DESIGN (PD)

Beyond Place N Route.

Ownership mode Physical Design from RTL to Power, Performance and Area optimized GDS. Expertise in FinFET-based nanometer-scale technology nodes and industry leading tool flows to bring precision and predictability to your complex physical implementation requirements.

Do it right with Ignitarium.

Our Offerings

- Advanced-Node Implementations

- Flip-chip and Wire-bond designs

- Pad ring design and Bump planning

- Low power, Multi-voltage, Multi-island implementations

- Full-chip and Block-level Floor planning & Power planning

- Physical synthesis

- PPA aware Placement

- Advanced Clock-Tree implementations

- Power Integrity Closure

- Signal Integrity Closure

- Functional, Timing & DRV ECOs

- Full-chip and Block-level Timing Closure

- Physical Verification

- Chip Finishing

- Tape-out & Foundry Interface

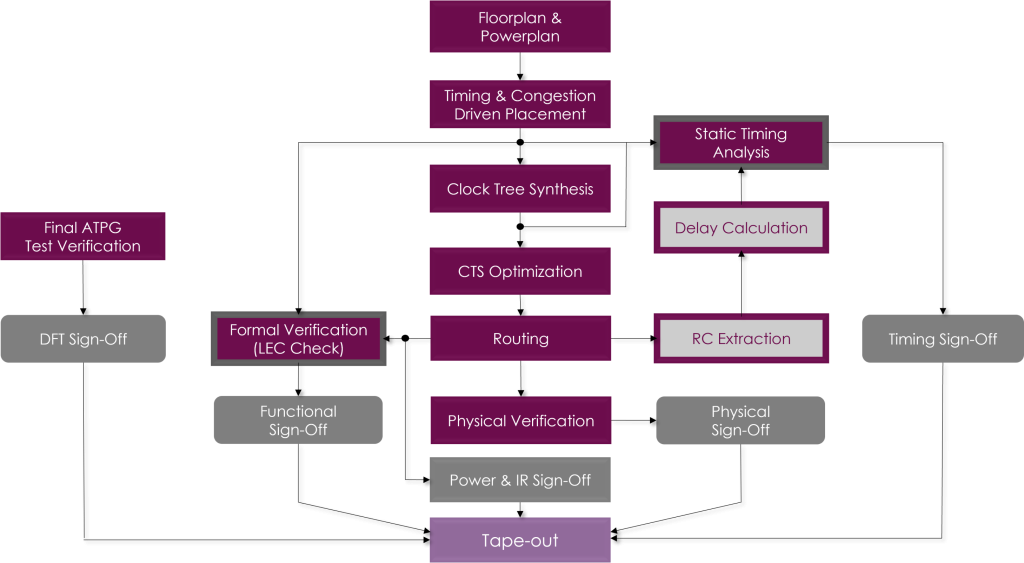

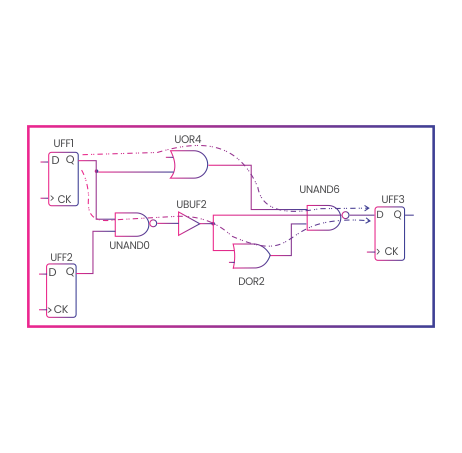

PD Stages

STAGE 01

In-bound Collateral QA

- Netlist integrity checks

- SDC integrity checks

- UPF integrity checks

- Library QA

- View QA (eg. LEF vs GDS)

- Tech file checks

- Rule file checks

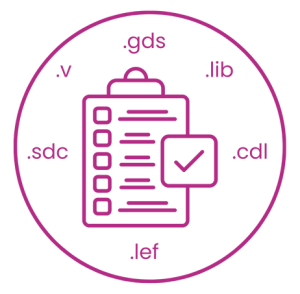

STAGE 02

IO Planning

- Define Bond Pad / Bump positions

- Create Pad ring / positions

- ESD Checks

- SSO Checks

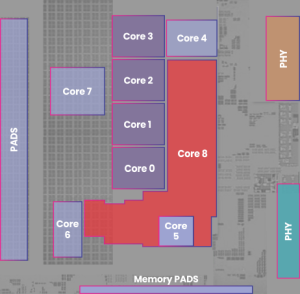

STAGE 03

Floor Planning

- Define Core and die dimensions

- Pin Placement

- Macro placement

- Halo assignment

- Cell pre-placement

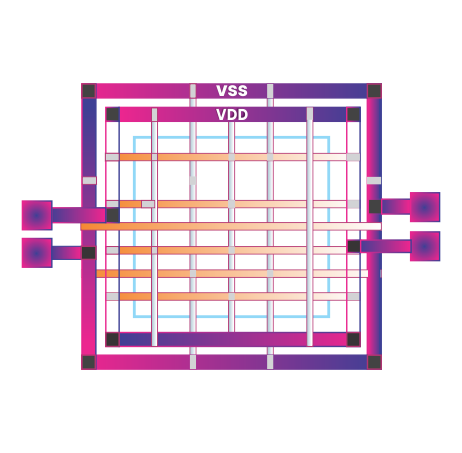

STAGE 04

Power Planning

- Connect Global nets

- Create Power Rings

- Create Power Stripes

- Create Special Routes

- Logic Equivalence Check

- IR, EM Analysis

- Physical Verification

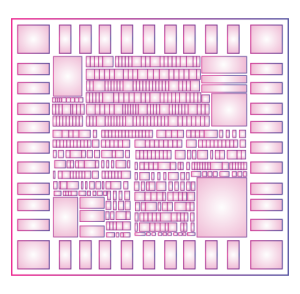

STAGE 05

Placement

- Coarse Placement

- Legalization

- High Fanout Net Synthesis

- Timing optimization

- Power optimization

- Scan-Chain Reordering

- Logic Equivalence Check

- Incremental Placement

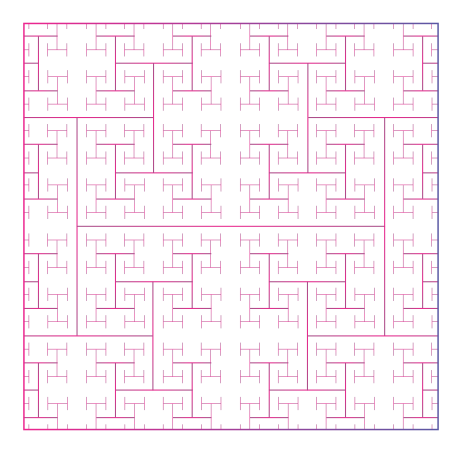

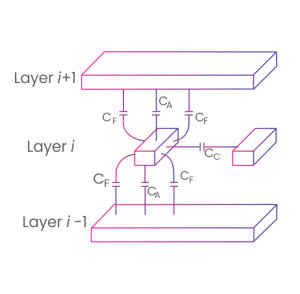

STAGE 06

Clock Tree Synthesis

- Timing Optimization

- Delay Balancing

- Latency Improvement

- DRV optimization

- Logic Equivalence Check

STAGE 07

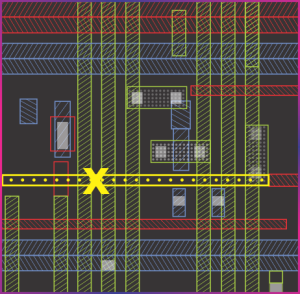

Routing

- Global Routing

- Track Assignment

- Detail Routing

- Search & Repair

- Incremental Routing

- Timing Analysis

STAGE 08

Fill & Finish

- Add Fillers

- Add PFC

- Add Metal Fill

- Add logo & fiducials

STAGE 09

Extraction

- Multi-interconnect corner RC correlation

- 2.5D or 3D extraction

- Detail RoSPEF generation uting

- SPEF generation

STAGE 10

Static Timing Analysis

- Set-up Check

- Hold Check

- DRV Check

- Pulse Width Check

- Duty Cycle Check

- Crosstalk Noise Check

- Crosstalk Delay Check

STAGE 11

IR & Power Analysis

- Static IR Drop

- Dynamic IR Drop

- Signal and Power EM

- Power Switch Coverage

- Secondary PG Coverage

- Static Power Analysis

- Dynamic Power Analysis

- Leakage Recovery

STAGE 12

Physical Verification

- ERC

- DRC

- LVS

- Density Checks

- XOR Checks

- DFM

STAGE 13

Tape-Out

- Base Layer Tapeout

- Metal Layer Tapeout

- Foundry interface

- e-Job view