Analog Mixed Signal (AMS) Verification

Eliminating every imperfection in the hazy boundary between Analog and Digital. (Other than Quantization Noise.)

Do it right with Ignitarium

Ignitarium's MSV Flow

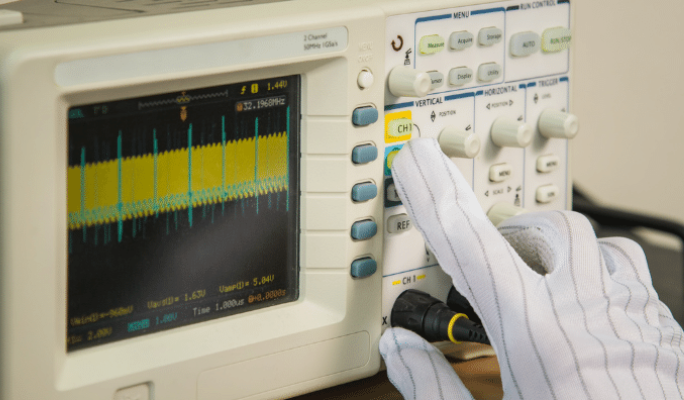

Analog Mixed Signal (AMS) Verification Stages

Step 1

Verification Planning

- Understand the Design Specification sheet and behavior of circuits (SPICE+RTL)

- Understand system level use cases

- Identify testcases that need to be run on block level and full chip level

- Identify signoff criteria

Step 2

Modeling

- Create models from specification or block level SPICE simulations

- Support a wide array of modeling languages namely Verilog-A / Verilog-AMS / Wreal / SV-RNM

- Check model vs schematic giving same stimuli/testbench and make sure they both are behaving similarly

- Consider tradeoffs in modeling between accuracy and speed based on intent of simulation and optionally add the effects of jitter / noise

Step 3

Methodology

- Block level or full chip testcases

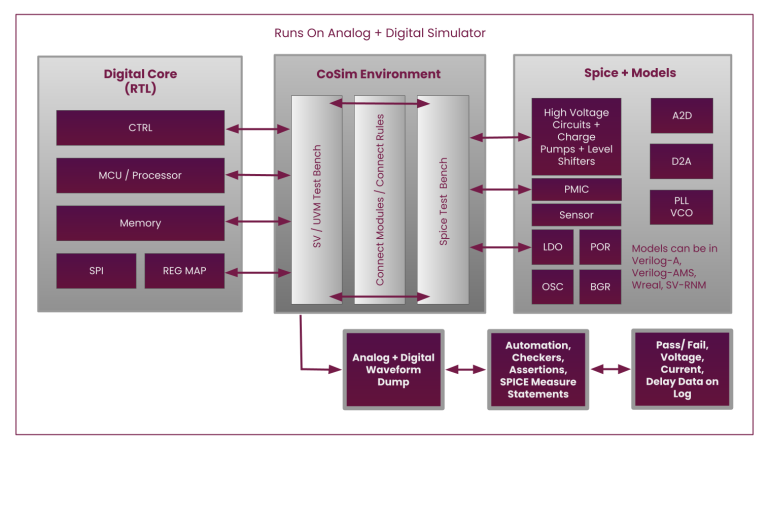

- AMS / CoSim methodology (SPICE+Models+RTL) (Digital + Analog Simulator). View flow diagram

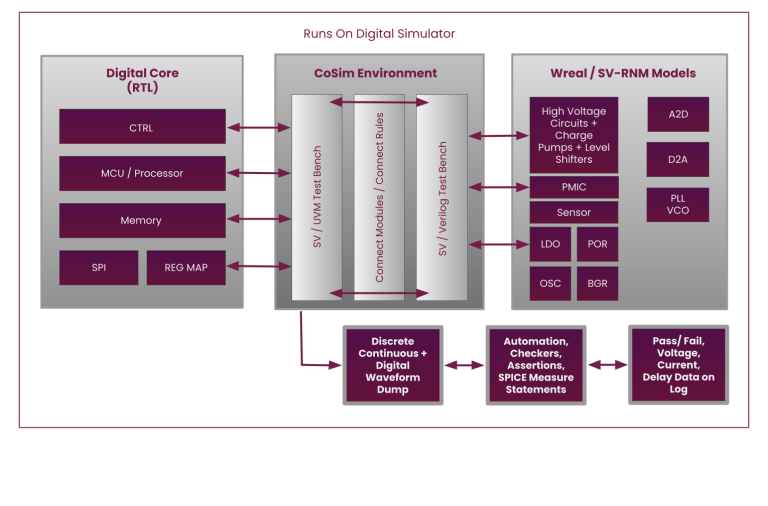

- DMS methodology, (RTL+Models(Wreal / RNM)) (Digital simulator). View flow diagram

Step 4

Automation

- Automating PASS / FAIL , currents, voltages, and delays to be viewed in logs

- Automation done using

- Consider tradeoffs in modeling between accuracy and speed based on intent of simulation and optionally add the effects of jitter / noise

- Assertions

- Checkers / SV tasks / functions

- SPICE measure statements

- Through scripts like python / perl / bash

-

Add coverage and randomization to cover all capabilities of digital in AMS verification

Case Studies

AMS VERIFICATION

Lithium Ion Battery Charger Mixed Signal Verification

Mixed Signal Verification using homegrown advanced AMS-verification framework for a Li-Ion battery charger ASIC.

Learn More

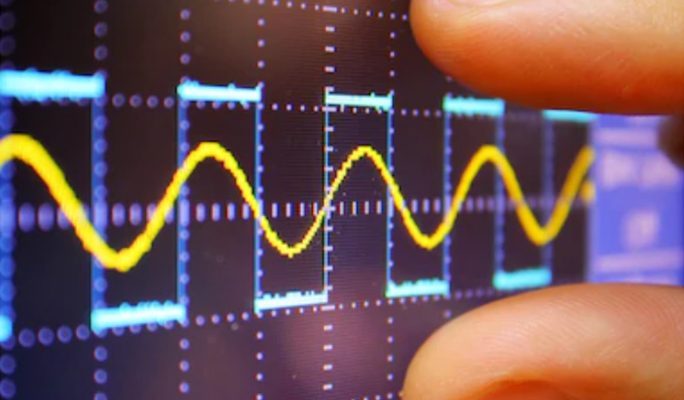

Co-Simulation / AMS Flow

DMS Flow

FAQs?

AMS Verification involves testing and validating integrated circuits (ICs) that contain both analog and digital components. It ensures that these complex systems meet functional specifications, performance requirements, and reliability standards, crucial for ensuring the integrity of mixed-signal designs.

Challenges include accurately modeling analog behavior, handling signal integrity issues, verifying interactions between analog and digital domains, and ensuring robustness against noise and environmental variations. Additionally, verifying complex interactions between analog and digital components presents unique testing complexities.

Common tools include SPICE simulators, AMS simulators, mixed-signal simulation environments, and hardware description languages like Verilog-AMS and VHDL-AMS. Verification methodologies such as co-simulation, assertion-based verification, and analog fault injection are widely utilized to ensure thorough testing coverage.

AMS Verification helps identify and rectify design flaws, ensuring that ICs meet stringent quality and reliability standards. It validates functionality across various operating conditions, mitigates risks associated with analog and mixed-signal design complexities, and enhances overall product reliability.

Advanced verification techniques, such as formal verification, analog behavioral modeling, and mixed-signal emulation, offer higher levels of design confidence, reduced time-to-market, and improved product quality. They enable comprehensive verification of complex AMS designs, leading to more robust and reliable ICs.