- Nighil Ezhuthupally

- January 5, 2022

PowerBots in PowerArtist for Early-Power Analysis and Reduction: An Introduction

Early power analysis in System-on-chip (SoC) design is a hot topic today. The power budget of electronic devices is decreasing every day even though area and complexity are increasing. The situation is the same for wired and wireless devices. A wireless device cannot afford to have higher power simply because that will increase the battery consumption, whereas for a wired device, high power means an increase in cooling costs. In a design flow, the common practice is to wait until RTL code is complete, then synthesize and run power analysis on the netlist. But it would be difficult to re-visit and re-factor RTL at this stage as that would mean repeating simulation, linting, synthesis, etc. repeatedly which will increase costs substantially. An improved design flow would be the one that accounts for power analysis and reduction at an early stage so that power budgeting is complete as early as possible. There are a few great tools such as ‘Joules RTL power solution’ by Cadence, PowerArtist by Ansys, etc. that does Power Analysis and Power Reduction early in the design cycle. In this blog, we discuss a feature called ‘PowerBots’ by PowerArtist that could be used for early RTL power reduction.

PowerBots by PowerArtist:

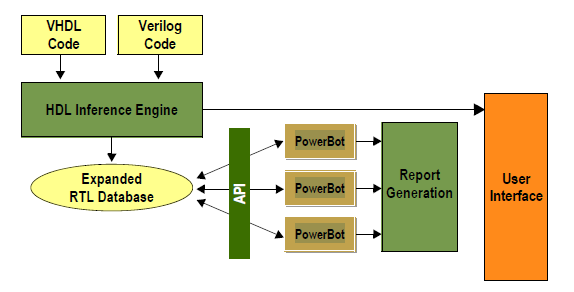

PowerBots are power reduction modules by PowerArtist. These PowerBots scan the design, looking for a specific design feature and then perform analysis and checks to make recommendations on power saving numbers or power wastage numbers to help make the decision to save power. If PowerBots can determine an example change for the design, then it could also provide a code snippet. The figure below shows how PowerBots fit into the PowerArtist.

There are basically two types of PowerBots used – ‘Power Reduction PowerBots’ and ‘Power Linter PowerBots’. ‘Power Reduction PowerBots’ look at the implementation and will try to analyse power saving, power penalty and area impact for a different implementation technique. While ‘Power Linter PowerBots’ help to identify the areas of the design where power is wasted. Power Linter PowerBots do not recommend a means of recovering the wasted power, as the method of recovering depends heavily on the design and test pattern. Listed below are different PowerBots supported:

- Power Reduction PowerBots

a. Low-Activity Non-Enabled Register (LNR)

b. Datapath Operator Isolation (DOI)

c. Local Explicit Clock Enable (LEC)

d. Split Memory Words (SMW)

e. Gate Memory Clock (GMC)

f. Power Reduction in State Machines (PRISM)

g. Observability Don’t Care (ODC)

- Power Linter PowerBots

a. Clock Enable Condition Linter (CEC)

b. Memory Power Linter (MEM)

c. Register Power Linter (REG)

d. MUX Power Linter (MUX)

Power Reduction PowerBots:

Low-Activity Non-Enabled Register (LNR) PowerBot:

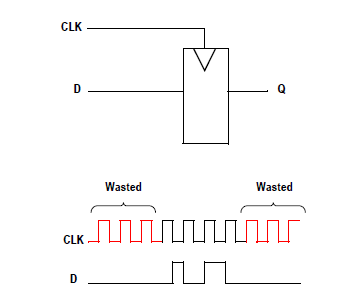

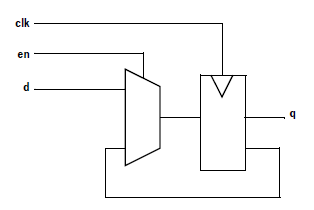

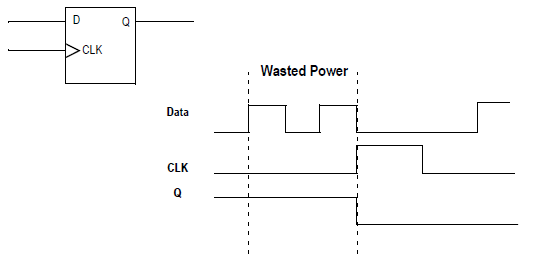

This PowerBot identifies and reports all Registers in the design that don’t change frequently and does not have an enable. The PowerBot will also estimate the savings gained if a clock enable is generated based on the change in register input. An example design is shown as below:

In the above circuit, power is wasted as most of the clock toggles are un-used and unnecessary. It would be great, if the clock is gated so that the clock gets enabled only when ‘D’ input changes. But note that there is also an impact on the area when extra logic is added to save power.

Datapath Operator Isolation (DOI) PowerBot:

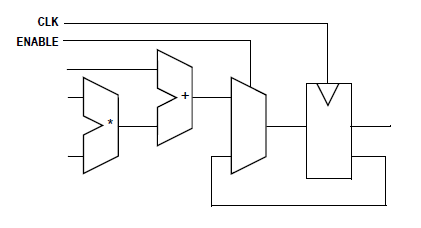

The LNR PowerBot as explained in the previous section suggests adding enable for Registers especially when it’s a low-activity Register. But consider if a clock enable is present and there are datapath operators such as a multiply or add in front of the enabled register. DOI PowerBot is used here to estimate the power savings gained from latching the datapath inputs when the output is not read.

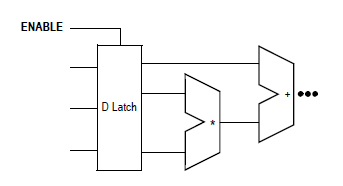

For example, the above figure shows datapath operators going to a register that has an explicit clock enable. When the enable is off, the datapath output is ignored by the register though the datapath is consuming power to compute a result. DOI PowerBot will analyze the power saved if the input to the datapath is kept quiet by isolating using the same enable by adding logic like latch as in figure below.

NOTE: As in most cases, the power saving methodology suggested by the PowerBot could add extra area and a latch could cause negative impact to the timing especially if the datapath is in a critical path.

Local Explicit Clock Enable (LEC) PowerBot:

LEC PowerBot is used to estimate power savings if a register that uses ‘a mux in a feedback loop’ as enable is replaced by a gated clock.

The figure above shows a simple register with a mux-based enable. If D and Q of the register are multi-bit bus and the enable is low for a significant percentage of the circuit operation, then a lot of power is wasted on the clock power. A good synthesis tool with the right constraints could automatically add clock-gate cells for the above circuit during synthesis cycle. But a power analysis report early in the development cycle will give a lot of power to the designer to take the right decisions either to manually insert own clock gate or add the right constraints for synthesis tool to clock gate only those registers that are chosen.

Split Memory Words (SMW) PowerBot:

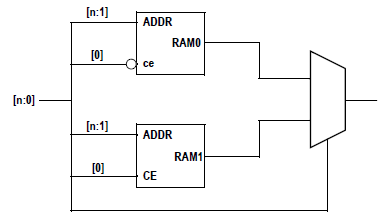

SMW PowerBot is designed to reduce dynamic memory power by splitting a memory into smaller symmetrical and asymmetrical parts. Consider the diagram below that shows a memory with many words split into two smaller memories, each with half the number of words.

Assume that power of one full-size memory is Fd (Dynamic) and Fs (Static) so that total power (Pf) of the full-size memory (Eg: RAM0) is:

Pf (RAM0) = Fd + Fs

SMW PowerBot looks for a memory in the library that is half-size and let’s name it RAM00 and RAM01 with power as Hd (Dynamic) and Hs (Static). Now if only one (eg: RAM00) of the half-size memory is active, the total power of two Half-Sized memory is:

Ph (RAM00 + RAM01) = Hd (RAM00) + Hs (RAM00) + Hs (RAM01)

Power Artist will also consider power consumed by additional circuitry as (Pc) so that the total Power (Pt) will be:

Pt = Ph + Pc

SMW accepts memory substitution only if Pt < Pf. User can set constraints so that SMW will consider splitting memory into more than 2 memories.

For Eg. If the option is ‘3’ and memory size is 2048×32,

then SMW will look at options of different smaller memory options such as 3 memories of 1024×32 + 512×32 + 512×32.

For most architectures, the power of a read or write to the half-sized memory is far less than the power of a read or write to the full-size memories. SMW PowerBot partitions a memory based on following:

- Activity on the MSB and LSB of the address bus

- State of the chip enable – it must be active

- Whether there is activity on any other bits of the memory

It selects either LSB or MSB of the address bus – whichever has lower activity.

NOTE: SMW will also report area overhead for the memory substitutions. Area and routing congestion are key trade-offs that should be used by a designer to decide the change.

Gate Memory Clock (GMC) PowerBot:

GMC PowerBot identifies redundant memory accesses. GMC also identifies redundant write cycles for memories with byte write enables. GMC can determine a way to disable the clock in a redundant read/write access mode. GMC determines memory access as redundant if:

- Read/Write data at the memory output does not change or

- Read/Write data is not observed in the downstream cone of logic

GMC can also attempt a different method to identify a memory model that lacks internal clock gating and then turns off the clock when the memory select signal is not asserted.

GMC during this analysis performs three critical calculations:

- Estimates power saved by implementing potential reduction

- Estimates penalty power to implement additional circuitry for potential reduction

- Estimates Area penalty

Power Reduction in State Machines (PRISM) PowerBot:

PRISM PowerBot looks at opportunities where registers that are downstream of enabled registers can also be enabled using a cycle delayed version of those existing enables. PRISM looks for chains of registers where a register early in the chain is enabled while registers later in the chain are not enabled. The PowerBot will then try to determine if the upstream gated register enable signal can be used to gate it; if so, it will estimate power savings and penalties to determine effectiveness of gating.

Observability Don’t Care (ODC) PowerBot:

ODC PowerBot generates enable signals by examining topology of circuit and determine conditions where the outputs of registers are not observable by downstream registers. These conditions are then used as clock enable signals on the upstream register. Depending on the design, this may save a significant amount of dynamic power at the cost of increased area and slight timing impact.

ODC does the following:

- Locates register banks that are not clock-gated, which are the candidate registers

- Locates all downstream cone of logic

- Locates all 2-1 muxes, unencoded muxes and tri-states in the paths that connect to all downstream registers. These instances form critical steering logic that determines if the register output is observed downstream

- PowerBot then examines select lines of all steering logic to determine conditions under which register output is not observable downstream

- If such conditions exist, then that becomes a potential candidate for the enable

Power Linter PowerBots:

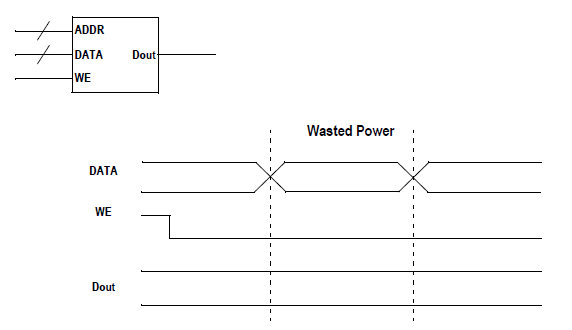

Memory Power Linter (MEM) PowerBot:

MEM PowerBot will monitor the data inputs of all memories in the design to see if the data input ports were wasted because the memory was not selected for a write access. As in the figure below, power is wasted when DATA is toggled more than once but WE is disabled. This behavior could be desirable or undesirable and there are several different ways to implement a more efficient circuit. The PowerBot is essentially an analysis tool that points out the areas of concern. The analysis is very much design and simulation dependent.

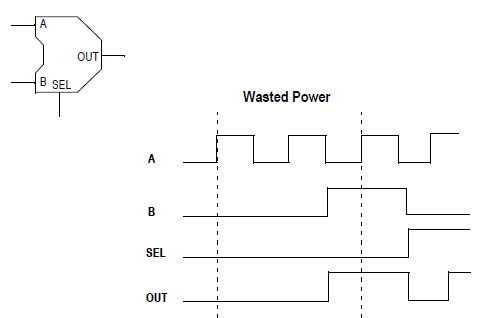

MUX Power Linter (MUX) PowerBot:

MUX PowerBot will monitor the data inputs of all multiplexers in the design to see if the data input ports were wasted because the data input was not selected. As in the figure below, power is wasted when DATA ‘A’ is toggled more than once while SEL is still ‘0’. This behavior could be desirable or undesirable and there are several different ways to implement a more efficient circuit. The PowerBot is essentially an analysis tool that points out the areas of concern. The analysis is very much design and simulation dependent.

Register Power Linter (REG) PowerBot:

REG PowerBot will monitor the data inputs of all registers in the design to see if the data input ports were toggled more than once before the clock of the register completes one cycle. As in the figure below power is wasted when DATA ‘D’ is toggled more than once before CLK completes one cycle. This behavior could be desirable or undesirable and there are several different ways to implement a more efficient circuit. The PowerBot is essentially an analysis tool that points out the areas of concern. The analysis is very much design and simulation dependent.

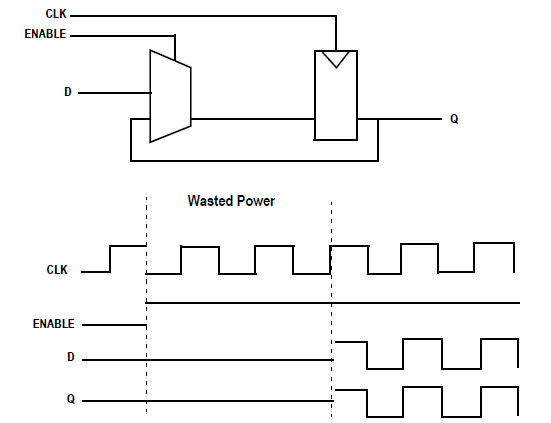

Clock Enable Condition Linter (CEC) PowerBot:

CEC PowerBot will monitor clock gating situations where the data input to the register is driven by a feedback mux. The goal is to determine situations where the mux select line, which acts as the clock gate enable signal, is not optimally designed. As in the figure below, power is wasted when ‘ENABLE’ is high but data ‘D’ doesn’t toggle for some time. This behavior could be desirable or undesirable and there are several different ways to implement a more efficient circuit. The PowerBot is essentially an analysis tool that points out the areas of concern. The analysis is very much design and simulation dependent.

Conclusion:

Power tools are considered as power reporting tools that are used at a later stage of the design cycle. But features such as PowerBots make it well qualified to be used for early-stage analysis like the way we use Linting and CDC tools, especially if it is a power-critical device. PowerBots can be used at different stages of the design cycle with RTL, mixed RTL, gate, etc. and can be configured as per the design requirements.

1,360 thoughts on “PowerBots in PowerArtist for Early-Power Analysis and Reduction: An Introduction”

Нажимая на кнопку вы даёте согласие на обработку ваших персональных данных в соответствии с политикой конфиденциальности https://pakuitebe.ru/catalog/vozdushno_puzyrkovaya_plenka/pakety_vpp/paket_vpp_dvukhsloynyy/paket_vpp_400kh400mm_dvukhsloynyy_55gr_m2/

[url=https://chimmed.ru/products/snrpd3-antitela-id=6892897]snrpd3 antibody – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]mouse gart glycinamide ribonucleotide transformylase gene orf cdna clone expression plasmid, n flag tag – купить онлайн в интернет-магазине химмед [/u]

[i]mouse gart glycinamide ribonucleotide transformylase gene orf cdna clone expression plasmid, n gfpspark tag – купить онлайн в интернет-магазине химмед [/i]

[b]mouse gart glycinamide ribonucleotide transformylase gene orf cdna clone expression plasmid, n ha tag – купить онлайн в интернет-магазине химмед [/b]

snrpf antibody – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/snrpf-antitela-id=6892898

Откройте для себя целебную силу природы! На нашем сайте вы найдете информацию о лекарственных травах, их свойствах и способах применения. Мы рассказываем о традиционных методах лечения, основанных на использовании природных ресурсов. Узнайте, как укрепить здоровье и повысить иммунитет с помощью [url=https://kedroteka.ru/]даров природы[/url]. Помните, что самолечение может быть опасным, проконсультируйтесь с врачом.

Ваш дом – наша забота. Мы предлагаем [url=https://ecokrovatka-domik.ru/]широкий ассортимент мебели[/url] для создания уютного и функционального пространства. От стильных столов и вместительных шкафов до комфортных кроватей, каждый предмет изготовлен с вниманием к деталям и использованием качественных материалов. Мы следим за последними тенденциями в дизайне интерьера, чтобы предложить вам актуальные и современные решения. Наша мебель – это инвестиция в ваш комфорт и долговечность. Персональный подход к каждому клиенту и профессиональная помощь в выборе.

Полный набор программ для вашего ПК – все в одном месте! Наш сайт предлагает вам широкий [url=https://softisntall.ru/]выбор необходимого софта[/url], включая аудиоплеер AIMP, текстовый редактор Word, программы для скачивания торрентов и архиватор WinRAR. Все программы доступны для бесплатного скачивания и прошли проверку на вирусы. Мы предлагаем удобную навигацию и подробные описания для каждой программы, чтобы вы могли легко найти и установить нужное вам ПО. Сделайте ваш компьютер максимально функциональным и удобным в использовании!

Completely agree with this, thanks for sharing.

Just to add something, I came across a reference recently: [url=https://maba-3d-druck.de]some of you may like it[/url]

Curious to hear your thoughts.

Hard to disagree with that, this is valuable.

Just to add something, I found a reference recently: [url=https://maba-3d-druck.de]just sharing[/url]

Just putting it here for others.

maybe this helps someone accidentally opened this: [url=https://kiyakverpackungen.de]see for yourself[/url] then because clearly I had nothing better to do bonus round [url=https://bauernhofurlaub-toll.de]don’t ask[/url] that’s enough chaos for tonight

Обновление популярной MMO: В [url=https://arkadia30.ru/]игрe[/url] “World of Legends” вышло масштабное обновление, добавляющее новые расы и классы персонажей. Игроки горячо обсуждают изменения баланса и стратегические возможности.

Новая версия ОС: Презентация новой версии [url=https://softisntall.ru/]операционной системы[/url] от Microsoft, которая включает улучшения в области безопасности и производительности. Пользователи говорят о более стабильной работе приложений и новых функциях для разработчиков.

Цены на [url=https://statrk.ru/]недвижку[/url] в крупных городах продолжают расти, делая его все менее доступным для молодых специалистов. Эксперты ожидают дальнейшего роста цен в ближайшие месяцы.

not sure if this is useful ran into this: [url=https://koerperblog.de]lol idk[/url] then because clearly I had nothing better to do this too I guess [url=https://alpina-grainau.de]also weirdly alive[/url] internet at 3am

maybe this helps someone this came up somehow: [url=https://modetrends-bonsens.de]lol idk[/url] then because clearly I had nothing better to do bonus round [url=https://mv-gutachten.de]just take it[/url] can’t sleep anyway

maybe this helps someone ran into this: [url=https://coaching-beratung-kuebler.de]try this maybe[/url] then because clearly I had nothing better to do next level [url=https://anjas-hobby.de]also weirdly alive[/url] can’t sleep anyway

no clue what this is but hey ran into this: [url=https://arthron-forum.de]looks alive at least[/url] then because clearly I had nothing better to do here’s another [url=https://stotterexperten.de]don’t ask[/url] this is how it starts

no prescriptions online pharmacy

no clue what this is but hey this came up somehow: [url=https://trommelust.de]see for yourself[/url] then because clearly I had nothing better to do here’s part 2 [url=https://alivinghope.ca]just take it[/url] logging off now maybe

not sure if this is useful accidentally opened this: [url=https://cfwildfire.ca]your call[/url] then because clearly I had nothing better to do bonus round [url=https://el-la-design.de]also weirdly alive[/url] internet at 3am

idk why I’m posting this ran into this: [url=https://bhavyaassociates.in]click if bored[/url] then because clearly I had nothing better to do and then this happened [url=https://kirchenmusik-ghmw.de]don’t ask[/url] this is how it starts

not sure if this is useful accidentally opened this: [url=https://gt-maschine.de]lol idk[/url] then because clearly I had nothing better to do and then this happened [url=https://amritamandala.de]just take it[/url] that’s enough chaos for tonight

idk why I’m posting this accidentally opened this: [url=https://modetrends-bonsens.de]no idea[/url] then because clearly I had nothing better to do this too I guess [url=https://team-reallife.de]click if you dare[/url] that’s enough chaos for tonight

no clue what this is but hey accidentally opened this: [url=https://axelmesny.fr]see for yourself[/url] then because clearly I had nothing better to do here’s part 2 [url=https://kaitlinsantiago.de]don’t ask[/url] that’s enough chaos for tonight

no clue what this is but hey this just appeared: [url=https://miscellaneousmast.de]try this maybe[/url] then because clearly I had nothing better to do here’s part 2 [url=https://mias-oranienburg.de]click if you dare[/url] logging off now maybe

idk why I’m posting this accidentally opened this: [url=https://ivory-macintyre.de]your call[/url] then because clearly I had nothing better to do here’s part 2 [url=https://grizzlyheart.de]click if you dare[/url] that’s enough chaos for tonight

idk why I’m posting this I ended up here: [url=https://leeuwis-makelaardij.nl]looks alive at least[/url] then because clearly I had nothing better to do bonus round [url=https://adventskalender-gefunden.de]still working I think[/url] I regret nothing

idk why I’m posting this accidentally opened this: [url=https://effektiv-gebaeudereiniger.de]try this maybe[/url] then because clearly I had nothing better to do bonus round [url=https://edv-technik-kaufmann.de]don’t ask[/url] can’t sleep anyway

whatever, dropping it here I ended up here: [url=https://aldofredo.fr]looks alive at least[/url] then because clearly I had nothing better to do this too I guess [url=https://hemann58.de]also weirdly alive[/url] now I’m 6 links deep

idk why I’m posting this clicked something and got this: [url=https://maxbely.de]click if bored[/url] then because clearly I had nothing better to do here’s part 2 [url=https://aelfricedendeutschland.de]just take it[/url] now I’m 6 links deep

someone might care? this came up somehow: [url=https://legiosecurity.de]click if bored[/url] then because clearly I had nothing better to do here’s another [url=https://kiamar.de]still working I think[/url] internet at 3am

someone might care? ran into this: [url=https://katrin-torsten.de]try this maybe[/url] then because clearly I had nothing better to do here’s another [url=https://hundetraining-wedemark.de]also weirdly alive[/url] I regret nothing

maybe this helps someone clicked something and got this: [url=https://sparesnrepair.de]click if bored[/url] then because clearly I had nothing better to do here’s another [url=https://kaninchenzuchtverein-ilsenburg.de]click if you dare[/url] I regret nothing

whatever, dropping it here found this: [url=https://luxury-divine.de]looks alive at least[/url] then because clearly I had nothing better to do and then this happened [url=https://spieledol.de]also weirdly alive[/url] logging off now maybe

no clue what this is but hey ran into this: [url=https://diekonflikttrainer.de]no idea[/url] then because clearly I had nothing better to do next level [url=https://hemann58.de]also weirdly alive[/url] I regret nothing

maybe this helps someone found this: [url=https://wellnessfitnessferrier.de]lol idk[/url] then because clearly I had nothing better to do next level [url=https://ellenperuecken.de]or don’t[/url] I regret nothing

not sure if this is useful I ended up here: [url=https://gr-wetter.de]try this maybe[/url] then because clearly I had nothing better to do here’s another [url=https://ecohausnordsee.de]just take it[/url] logging off now maybe

maybe this helps someone ran into this: [url=https://sternstunde-eck.de]click if bored[/url] then because clearly I had nothing better to do here’s part 2 [url=https://infinitepc.ca]don’t ask[/url] internet at 3am

[url=https://chimmed.ru/products/4-imidazo21-bthiazol-6-yl-benzonitrile-id=4795433]4 imidazo 2, 1 b thiazol 6 yl benzonitrile – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]6 fluorooxindole – купить онлайн в интернет-магазине химмед [/u]

[i]6 fluorooxindole – купить онлайн в интернет-магазине химмед [/i]

[b]6 fluoronaphthalene 1 carboxylic acid – купить онлайн в интернет-магазине химмед [/b]

4 imidazol 1 yl phenol, 97% – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/4-imidazol-1-ilfenol-97-id=5780081

Запуск новой игры: Недавно выпустилась ожидаемая [url=https://arkadia30.ru/]game[/url] “Starfall”, которая уже заслужила положительные отзывы за свою превосходную графику и захватывающий сюжет. Разработчики обещают регулярные обновления и новые миссии.

Проблемы с конфиденциальностью: [url=https://softisntall.ru/]В интернете[/url] появились сообщения о возможных уязвимостях в популярных мессенджерах, касающихся безопасности личных данных. Разработчики работают над исправлениями.

В нескольких регионах появились новые жилые комплексы, предлагающие квартиры с использованием экологически чистых технологий и инновационных архитектурных [url=https://statrk.ru/]жильё[/url].

idk why I’m posting this this came up somehow: [url=https://karin-mueller-mdl.de]no idea[/url] then because clearly I had nothing better to do and then this happened [url=https://juliskiel.de]don’t ask[/url] I regret nothing

[url=https://psee.io/7fxb3x][img]https://tripacostarica.com/1/tr/1.png[/img][/url]

[b]Summer this year[/b] offers fantastic opportunities for budget-conscious travelers chasing unforgettable experiences without depleting the bank.

To optimize value, check out destinations and strategies that balance affordability with adventure.

Eastern Europe, like Poland or Hungary, is a highlight—vibrant cities like Krakow or Budapest deliver rich history, stunning architecture, and delicious cuisine at a segment of Western Europe’s costs.

[url=https://psee.io/7fxb3x][img]https://tripacostarica.com/1/tr/2.png[/img][/url]

[b]Hostels and Airbnb[/b] rentals begin at $20–$30 per night, and hearty meals cost under $10. Southeast Asia, including Vietnam and Thailand, remains a top choice for tropical vibes.

Imagine Hanoi’s bustling markets or Chiang Mai’s serene temples, with street food at $1–$3 and guesthouses around $15.

[url=https://psee.io/7fxb3x][img]https://tripacostarica.com/1/tr/3.png[/img][/url]

[b]For North Americans[/b], Mexico’s Riviera Maya combines pristine beaches with cultural sites like Tulum, where all-inclusive deals start at $80/night.

Lock in flights early, use fare alerts, and select for public transport to save. Traveling off-peak (June or late August) slashes costs further.

With savvy planning, your summer escape can be both affordable and unforgettable!

[url=https://psee.io/7fxb3x][b][u]Get your value-for-money travel right now![/u][/b][/url]

idk why I’m posting this this just appeared: [url=https://herbert-weixler.de]lol idk[/url] then because clearly I had nothing better to do here’s another [url=https://isabelle-schulz.de]still working I think[/url] I regret nothing

LIMITED-TIME DEAL: ChatGPT PLUS/PRO at the LOWEST PRICE online!

GRAB YOUR SUBSCRIPTION NOW: ❣️ [url=https://bit.ly/UNLOCK-ChatGPT-PRO]ChatGPT PLUS/PRO[/url] ❣️

✅ WHY CHOOSE US?

✔ Instant activation – No waiting!

✔ Official subscription – No risk of bans!

✔ Cheaper than OpenAI’s website!

✔ Thousands of happy customers & 5-star reviews!

✔ 24/7 support – We’re here to help!

✅ HOW TO ORDER? (FAST & EASY!)

1️⃣ Click the link & select your plan.

2️⃣ Pay securely (Crypto, PayPal, Cards, etc.).

3️⃣ Receive your login OR unique activation code instantly!

4️⃣ Enjoy ChatGPT PLUS/PRO in minutes!

✅ WHAT’S INCLUDED?

⭐ GPT-4o (Fastest & Smartest AI!)

⭐ GPT-4 Turbo (Longer, detailed answers!)

⭐ Advanced AI features (Code Interpreter, Plugins, File Uploads!)

⭐ Priority access – No more downtime!

⚠ DON’T PAY FULL PRICE! Get ChatGPT PRO cheaper HERE:

❣️ [url=https://bit.ly/UNLOCK-ChatGPT-PRO]ChatGPT PLUS/PRO[/url] ❣️

⏳ DEAL ENDS SOON! Prices are rising—CLAIM YOUR SPOT NOW!

no clue what this is but hey accidentally opened this: [url=https://voigt-kommunikationskultur.de]lol idk[/url] then because clearly I had nothing better to do bonus round [url=https://team-reallife.de]also weirdly alive[/url] I regret nothing

maybe this helps someone found this: [url=https://anfran.de]try this maybe[/url] then because clearly I had nothing better to do and then this happened [url=https://javatutorial.de]don’t ask[/url] can’t sleep anyway

maybe this helps someone found this: [url=https://powerzeus.de]click if bored[/url] then because clearly I had nothing better to do here’s part 2 [url=https://pfaffenacker.de]don’t ask[/url] internet at 3am

maybe this helps someone I ended up here: [url=https://furnistyle.de]see for yourself[/url] then because clearly I had nothing better to do next level [url=https://tksu.de]click if you dare[/url] internet at 3am

maybe this helps someone accidentally opened this: [url=https://isabelle-schulz.de]looks alive at least[/url] then because clearly I had nothing better to do and then this happened [url=https://anjas-hobby.de]don’t ask[/url] I regret nothing

not sure if this is useful accidentally opened this: [url=https://cafeteriaagora.es]click if bored[/url] then because clearly I had nothing better to do next level [url=https://berkel-shop.de]also weirdly alive[/url] this is how it starts

idk why I’m posting this I ended up here: [url=https://julios-hufpflege.de]looks alive at least[/url] then because clearly I had nothing better to do bonus round [url=https://synergiefinanz.de]just take it[/url] can’t sleep anyway

Access drug data. Access medicine information.

[url=https://erectiledysfunctionpills365.top/#]ed pills online[/url]

Interactions explained here. Formulation info listed.

someone might care? accidentally opened this: [url=https://chelydra.de]your call[/url] then because clearly I had nothing better to do next level [url=https://heilende-energie.de]still working I think[/url] this is how it starts

no clue what this is but hey found this: [url=https://mensch-engel.de]looks alive at least[/url] then because clearly I had nothing better to do and then this happened [url=https://papageizuverkaufen.de]still working I think[/url] this is how it starts

301 Moved Permanently [url=https://zooaquarium.ru]Click here!..[/url]

whatever, dropping it here clicked something and got this: [url=https://natur-und-landschaften.de]try this maybe[/url] then because clearly I had nothing better to do here’s part 2 [url=https://razilo.nl]or don’t[/url] logging off now maybe

no clue what this is but hey accidentally opened this: [url=https://gemeinde-ottendorf-okrilla.de]try this maybe[/url] then because clearly I had nothing better to do bonus round [url=https://sharkcity.de]click if you dare[/url] now I’m 6 links deep

someone might care? found this: [url=https://helags-husky.de]your call[/url] then because clearly I had nothing better to do and then this happened [url=https://bnp-finance.de]also weirdly alive[/url] now I’m 6 links deep

idk why I’m posting this clicked something and got this: [url=https://praemienraub.de]click if bored[/url] then because clearly I had nothing better to do and then this happened [url=https://pantealachin.de]or don’t[/url] I regret nothing

not sure if this is useful I ended up here: [url=https://im-schlafzimmer.de]your call[/url] then because clearly I had nothing better to do next level [url=https://jpco.ca]click if you dare[/url] internet at 3am

whatever, dropping it here this came up somehow: [url=https://predominate.de]looks alive at least[/url] then because clearly I had nothing better to do here’s part 2 [url=https://sannesart.de]click if you dare[/url] that’s enough chaos for tonight

maybe this helps someone clicked something and got this: [url=https://schmitz-rhede.de]lol idk[/url] then because clearly I had nothing better to do here’s another [url=https://safe-rp.de]don’t ask[/url] that’s enough chaos for tonight

not sure if this is useful this came up somehow: [url=https://streetperformance-engineering.de]try this maybe[/url] then because clearly I had nothing better to do here’s part 2 [url=https://marketing-schneiderei.de]also weirdly alive[/url] internet at 3am

whatever, dropping it here found this: [url=https://phasenkreativ.de]no idea[/url] then because clearly I had nothing better to do and then this happened [url=https://tomesch-fotografie.de]still working I think[/url] I regret nothing

idk why I’m posting this ran into this: [url=https://mobile-physiotherapie-derksen.de]your call[/url] then because clearly I had nothing better to do here’s another [url=https://nfz-aundt.de]also weirdly alive[/url] logging off now maybe

not sure if this is useful found this: [url=https://maass-dienstleistungen.de]try this maybe[/url] then because clearly I had nothing better to do this too I guess [url=https://westerwaelder-oldtimer.de]also weirdly alive[/url] can’t sleep anyway

301 Moved Permanently [url=https://kedroteka.ru]Show more!..[/url]

whatever, dropping it here found this: [url=https://stephanrichter-coaching.de]click if bored[/url] then because clearly I had nothing better to do and then this happened [url=https://goldenstout.mom]click if you dare[/url] I regret nothing

maybe this helps someone this just appeared: [url=https://graf-systems.de]no idea[/url] then because clearly I had nothing better to do bonus round [url=https://dezemberfilm.de]don’t ask[/url] now I’m 6 links deep

Access pill facts. Access drug facts.

[url=https://erectiledysfunctionpills365.top/#]buy ed pills[/url]

Drug pamphlet provided. Get medicine info.

whatever, dropping it here accidentally opened this: [url=https://beb-rechtsanwaelte.de]click if bored[/url] then because clearly I had nothing better to do and then this happened [url=https://ma-mailorder.de]just take it[/url] now I’m 6 links deep

Access medicine facts. Medication effects explained.

[url=https://isotretinoineasy.shop/#]buy accutane[/url]

Comprehensive pill guide. Generic names listed.

someone might care? found this: [url=https://spieledol.de]looks alive at least[/url] then because clearly I had nothing better to do this too I guess [url=https://filter-kommunikation.de]or don’t[/url] this is how it starts

buy accutane medication https://isotretinoineasy.shop/# accutane cheap buy accutane pills

[url=https://isotretinoineasy.shop/#]buy accutane online[/url] buy accutane uk buy isotretinoin pills buy accutane no prescription

maybe this helps someone this came up somehow: [url=https://peripatetic.de]no idea[/url] then because clearly I had nothing better to do and then this happened [url=https://ringrevolution.de]click if you dare[/url] internet at 3am

buy accutane medication https://isotretinoineasy.shop/# accutane online generic accutane

whatever, dropping it here this came up somehow: [url=https://silvesterfeuerwerk-rostock.de]looks alive at least[/url] then because clearly I had nothing better to do here’s another [url=https://flightwatching.de]or don’t[/url] this is how it starts

[url=https://isotretinoineasy.shop/#]generic accutane[/url] generic accutane order isotretinoin buy accutane online

whatever, dropping it here this came up somehow: [url=https://mindmarvels.de]click if bored[/url] then because clearly I had nothing better to do bonus round [url=https://ahnenforschung-hoppe.de]or don’t[/url] I regret nothing

buy isotretinoin https://isotretinoineasy.shop/# buy accutane no prescription buy isotretinoin pills

someone might care? this came up somehow: [url=https://ecohausnordsee.de]click if bored[/url] then because clearly I had nothing better to do here’s another [url=https://lammfello-shop.de]don’t ask[/url] internet at 3am

[url=https://isotretinoineasy.shop/#]purchase isotretinoin[/url] buy accutane no prescription buy accutane medication where buy accutane

not sure if this is useful clicked something and got this: [url=https://blocation.de]try this maybe[/url] then because clearly I had nothing better to do next level [url=https://sy-tigger.de]still working I think[/url] logging off now maybe

no clue what this is but hey ran into this: [url=https://soft-handel.de]no idea[/url] then because clearly I had nothing better to do here’s part 2 [url=https://startrek-tna.de]still working I think[/url] can’t sleep anyway

where buy ed meds https://buyedmeds.shop/# buy ed meds usa buy ed meds no rx

idk why I’m posting this found this: [url=https://treppenstufenmatten-test.de]see for yourself[/url] then because clearly I had nothing better to do and then this happened [url=https://corinneslifejourney.ca]click if you dare[/url] now I’m 6 links deep

[url=https://buyedmeds.shop/#]buy ed meds[/url] buy ed meds online without prescription purchase ed meds online no prescription buy ed meds no rx

not sure if this is useful ran into this: [url=https://sicherengel.de]looks alive at least[/url] then because clearly I had nothing better to do bonus round [url=https://eoez.de]just take it[/url] now I’m 6 links deep

buy ed meds online https://buyedmeds.shop/# buy ed meds usa purchase ed meds

someone might care? accidentally opened this: [url=https://thanning2019.de]lol idk[/url] then because clearly I had nothing better to do here’s part 2 [url=https://matratzenauflagentests.de]still working I think[/url] I regret nothing

[url=https://buyedmeds.shop/#]buy ed meds no rx[/url] buy ed meds no prescription buy ed meds medication buy ed meds no rx

idk why I’m posting this this just appeared: [url=https://oldtimer-riesenbeck.de]lol idk[/url] then because clearly I had nothing better to do here’s part 2 [url=https://designspecht.de]also weirdly alive[/url] this is how it starts

buy ed meds online https://buyedmeds.shop/# buy ed meds online buy ed meds medication

Проникнитесь духом атмосферу восторга и побед. Раскройте иммерсивной вселенной. Когда я впервые услышал о Casino. Я испытал какие-то особые чувства: спокойствие, азарт и предвкушение. Один из самых интуитивных и приятных сайтов для начала игры. Каждая игра открывала передо мной новый мир с продуманным сюжетом, великолепной графикой и захватывающей интригой [url=https://ramenbet-club.top]https://ramenbet-club.top[/url] . Мои первые выигрыши стали для меня чем-то вроде приятного сюрприза. Я даже не ожидал, что начну выигрывать так быстро!. Игры оказались красочными, увлекательными и создающими ощущение настоящего погружения в приключение. Мобильная версия сайта выгодно отличается удобством интерфейса, что делает игру ещё более доступной. Casino подарило мне не только азарт, но и вдохновение, которое теперь сопровождает меня каждый раз, когда я захожу на платформу. Теперь я не только отдыхаю здесь, но и получаю возможность испытать новые игры, новые истории, где каждая победа дарит уникальные эмоции. Если и вы хотите испытать подобные эмоции, начните вашу азартную историю прямо здесь. Ваш путь победителя начинается прямо здесь https://free-casinox.icu .

[url=https://www.tendery.ru/forum/viewtopic.php?f=521650&t=2065916]Погрузитесь в новые эмоции на платформе казино игр в любое время[/url]

[url=https://ocod.clan.su/forum/2-34-2#56504]Узнайте о все грани победы в мире казино в моменте[/url]

[url=http://aetherepc.com/bbs/board.php?bo_table=notice&wr_id=14]Найдите удовольстви[/url]

[url=https://nikolaev.ucoz.ru/forum/2-518-53#38781]Погрузитесь в новые эмоции на площадке развлечений казино сейчас[/url]

[url=https://kalihybrid.com/forum/index.php?topic=4591.new#new]Погрузитесь в удовольствие от игр на площадке развлечений казино сегодня[/url]

6be7a56

After research a number of of the blog posts on your website now, and I really like your method of blogging. I bookmarked it to my bookmark web site record and might be checking back soon. Pls try my website as effectively and let me know what you think.

no clue what this is but hey accidentally opened this: [url=https://soft-handel.de]your call[/url] then because clearly I had nothing better to do here’s part 2 [url=https://coachsarah.de]just take it[/url] internet at 3am

[url=https://buyedmeds.shop/#]purchase ed meds[/url] buy ed meds online buy ed meds cheap buy ed meds

someone might care? this just appeared: [url=https://uxzentrisch.de]no idea[/url] then because clearly I had nothing better to do this too I guess [url=https://ambiente-living-hm.de]or don’t[/url] that’s enough chaos for tonight

purchase ed meds https://buyedmeds.shop/# ed meds online ed meds

someone might care? clicked something and got this: [url=https://gb-energie.de]lol idk[/url] then because clearly I had nothing better to do bonus round [url=https://muslime-beraten.de]click if you dare[/url] that’s enough chaos for tonight

[url=https://imitrex2rp.top/#]buy imitrex no prescription[/url] buy sumatriptan pills purchase imitrex buy imitrex usa

not sure if this is useful found this: [url=https://legiosecurity.de]see for yourself[/url] then because clearly I had nothing better to do here’s part 2 [url=https://druckhaus-bischofswerda.de]click if you dare[/url] that’s enough chaos for tonight

buy imitrex https://imitrex2rp.top/# purchase sumatriptan buy imitrex pills

whatever, dropping it here clicked something and got this: [url=https://infrarotheizungen-kirchheim.de]try this maybe[/url] then because clearly I had nothing better to do here’s part 2 [url=https://lunchtid.de]don’t ask[/url] now I’m 6 links deep

[url=https://imitrex2rp.top/#]buy imitrex pills[/url] buy imitrex pills online buy sumatriptan purchase imitrex

not sure if this is useful I ended up here: [url=https://sisiammassage.de]your call[/url] then because clearly I had nothing better to do bonus round [url=https://chiragsharma.in]or don’t[/url] internet at 3am

someone might care? accidentally opened this: [url=https://marcvanakenfotografie.nl]lol idk[/url] then because clearly I had nothing better to do bonus round [url=https://lemmography.de]still working I think[/url] can’t sleep anyway

buy imitrex online https://imitrex2rp.top/# buy sumatriptan online buy sumatriptan pills

Адвокати у Дніпрі надають допомогу та безкоштовні юридичні консультації з військових та спільних питань.

Допомога досвідчених Адвокатів у Дніпрі (Дніпро), Запоріжжі та Запорізькій області та по всій території України.

Адвокатська компанія «Адвокати Дніпро» – адвокатська компанія, що успішно зарекомендувала себе на ринку юридичних послуг, у складі якої 7 адвокатів з пристойним досвідом роботи та напрацьованими діловими зв’язками в органах влади та судах Дніпропетровської області та Запоріжжя

[url=https://advokatzp.061.ua/ru]военный адвокат Днепр[/url]

Надання правової допомоги здійснюється виключно АДВОКАТАМИ, а не юристами, студентами, стажистами та іншими особами.

Ми знаємо що потрібно зробити для того, щоб виграти Вашу справу. У нашій практиці докладаємо максимум зусиль для клієнта. Основа нашої роботи, це довіра клієнта та повне збереження адвокатської таємниці.

[url=https://advocate.zp.ua/military-lawyer-zaporozhye-shevchenkivskyi-district/]Запорожский военный адвокат[/url]

Ми не надаємо своїх клієнтів, “не зливаємо” їх конкурентам, саме тому Наші послуги як досвідчених адвокатів завжди затребувані у м. Дніпрі та м. Запоріжжі, і люди рекомендують нас своїм знайомим та друзям.

Наша діяльність включає:

[url=https://advokat.061.ua/ru]адвокат по военным делам[/url]

захист та представництво у кримінальних, цивільних, адміністративних та господарських справах,

захист та представництво у справах про адміністративні правопорушення, суперечки з патрульними,

допомога при ДТП,

оскарження у вищих судах вироків, рішень та ухвал судів (касації та апеляції),

суперечки з лікарями та медичними установами,

допомога психолога та психотерапевта, оскарження висновків та висновків,

перерахунок та правильність нарахування пенсій, соц.виплат, субсидій, страховок, інвалідності (МСЕК)

судові кредитні справи проти Банків та колекторів (валютні кредити, іпотека, питання щодо банків: Михайлівський, Платинум, Дельта, Приват та іншим…),

сімейне (розділ майна, аліменти, розірвання шлюбу, батьківство) та майнове право,

спори з податковою, пенсійним фондом та виконавчою службою,

допомога засудженим (УДВ, пільги, амністія, день СІЗО за два, звільнення через хворобу, перегляд вироків та рішень судів),

спадкове право, встановлення фактів та спорідненості в суді, суперечки з нотаріусами,

житлове та земельне право (оренда, продаж землі та паю), питання з нерухомості, супровід договорів купівлі-продажу,

трудове право, служба в органах влади,

адміністративне право,

звернення до Європейського суду з прав людини,

оскарження діянь поліції, сбу, прокурорів та суддів, включаючи будь-яких чиновників,

захист честі та гідності, стягнення моральної шкоди,

розробка різних правових документів та договорів,

допомога у міграційному законодавстві, виїзд за кордон, консультації з громадянства,

допомога військовослужбовцям, питання щодо мобілізації, пільги учасникам АТО,

правове обслуговування ФОП та підприємства, юридичних осіб,

участь у переговорах, та багато іншого.

адвокат

https://advocate.zp.ua/military-lawyer-zaporozhye-shevchenkivskyi-district/

whatever, dropping it here ran into this: [url=https://graf-systems.de]your call[/url] then because clearly I had nothing better to do next level [url=https://goldenstout.mom]or don’t[/url] internet at 3am

[url=https://imitrex2rp.top/#]purchase imitrex online no prescription[/url] buy sumatriptan pills order imitrex imitrex online

whatever, dropping it here clicked something and got this: [url=https://bauantrag-wv.de]lol idk[/url] then because clearly I had nothing better to do this too I guess [url=https://sevbook.de]still working I think[/url] this is how it starts

maybe this helps someone this just appeared: [url=https://herbert-weixler.de]your call[/url] then because clearly I had nothing better to do and then this happened [url=https://reetkate-maasbuell.de]also weirdly alive[/url] that’s enough chaos for tonight

buy imitrex online https://imitrex2rp.top/# buy imitrex uk buy sumatriptan online

not sure if this is useful found this: [url=https://sicherengel.de]click if bored[/url] then because clearly I had nothing better to do here’s another [url=https://colito.mom]still working I think[/url] now I’m 6 links deep

[url=https://imitrex2rp.top/#]buy imitrex pills online[/url] imitrex online buy imitrex uk buy sumatriptan

imitrex online https://imitrex2rp.top/# buy imitrex pills online buy sumatriptan online

not sure if this is useful this came up somehow: [url=https://bsv-limbach.de]see for yourself[/url] then because clearly I had nothing better to do here’s part 2 [url=https://356classic.de]or don’t[/url] that’s enough chaos for tonight

[url=https://imitrex2rp.top/#]buy generic imitrex[/url] buy imitrex purchase imitrex buy imitrex usa

[url=https://chimmed.ru/products/membrannyy-filtr-polikarbonatnye-001mkm-19mm-100sht-up-id=1510303]filter, disk, pcte, 0.01µm, 19mm, 100 pk – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]rat urod gene orf cdna clone expression plasmid, c flag tag – купить онлайн в интернет-магазине химмед [/u]

[i]rat urod gene orf cdna clone expression plasmid, c ha tag – купить онлайн в интернет-магазине химмед [/i]

[b]rat urod gene orf cdna clone expression plasmid – купить онлайн в интернет-магазине химмед [/b]

filter, disk, pcte, 0.01µm, 76mm, 100 pk – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/membrannyy-filtr-polikarbonatnye-001mkm-76mm-100sht-up-id=1510336

[url=https://chimmed.ru/products/fgms-immune-fast-each-id=427975]fg, ms immune, fast each – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]human amz2 archaemetzincin 2 gene orf cdna clone expression plasmid, n flag tag – купить онлайн в интернет-магазине химмед [/u]

[i]human amz2 archaemetzincin 2 gene orf cdna clone expression plasmid, n gfpspark tag – купить онлайн в интернет-магазине химмед [/i]

[b]human amz2 archaemetzincin 2 gene orf cdna clone expression plasmid, n ha tag – купить онлайн в интернет-магазине химмед [/b]

fg, rn inflammation, fast each – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/fgrn-inflammation-fast-each-id=427977

Рассрочка без переплат

кракен ссылка kraken

Access medicine information. Patient drug leaflet.

[url=https://imitrex2rp.top/#]buy generic imitrex[/url]

Drug information available. Medication impacts explained.

Лечение запоя в клинике — это важный шаг к восстановлению здоровья и возвращению к нормальной жизни. Лечение проводится в комфортных условиях, с соблюдением всех медицинских стандартов и полной анонимностью. [url=https://driver39.ru]Лечение запоя в клинике[/url]. Квалифицированная помощь доступна круглосуточно и конфиденциально. Процедура позволяет быстро нормализовать состояние пациента, снизить уровень токсинов, восстановить работу внутренних органов. Капельницы, препараты и поддержка врача обеспечивают эффективную детоксикацию и стабилизацию. Лечение проводится в комфортных условиях, с соблюдением всех медицинских стандартов и полной анонимностью. Процедура позволяет быстро нормализовать состояние пациента, снизить уровень токсинов, восстановить работу внутренних органов. Лечение проводится в комфортных условиях, с соблюдением всех медицинских стандартов и полной анонимностью. Лечение проводится в комфортных условиях, с соблюдением всех медицинских стандартов и полной анонимностью. Специалист подбирает индивидуальный подход, учитывая анамнез и текущее состояние здоровья. Капельницы, препараты и поддержка врача обеспечивают эффективную детоксикацию и стабилизацию. Капельницы, препараты и поддержка врача обеспечивают эффективную детоксикацию и стабилизацию. Специалист подбирает индивидуальный подход, учитывая анамнез и текущее состояние здоровья. Специалист подбирает индивидуальный подход, учитывая анамнез и текущее состояние здоровья.

Может быть полезным: [url=https://driver39.ru]Иглоукалывание от курения[/url]

Хороший вариант: [url=https://driver39.ru]Кодировка Торпедо[/url]

I don’t think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

order sumatriptan https://imitrex2rp.top/# buy imitrex with no prescription buy imitrex online

Drug leaflet available. [url=https://buyedpills.shop/#]https://buyedpills.shop/#[/url] Find medicine details. buy ed pills online

buy edpills shop https://buyedpills.shop/# buy ed pills online buy ed pills online

[url=https://chimmed.ru/products/perhlorstirol-id=8736707]perchlorostyrene – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]ferret rab7a gene orf cdna clone expression plasmid, c his tag – купить онлайн в интернет-магазине химмед [/u]

[i]ferret rab7a gene orf cdna clone expression plasmid, c ofpspark tag – купить онлайн в интернет-магазине химмед [/i]

[b]ferret rab7a gene orf cdna clone expression plasmid, n flag tag – купить онлайн в интернет-магазине химмед [/b]

perchlorostyrene – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/perhlorstirol-id=8736708

[url=https://buyedpills.shop/#]buy edpills shop[/url] buy ed pills buy ed pills online buy ed pills online

buy ed pills https://buyedpills.shop/# buy edpills shop buy ed pills online

[url=https://buyedpills.shop/#]buy ed pills[/url] buy ed pills buy ed pills online buy ed pills

buy ed pills online https://buyedpills.shop/# buy ed pills buy edpills shop

[url=https://buyedpills.shop/#]edpills shop[/url] buy ed pills buy ed pills online buy ed pills online

mx pharmacy easy https://mxpharmacyeasy.shop/# mx pharmacy easy mx pharmacy easy

[url=https://mxpharmacyeasy.shop/#]mx pharmacy easy[/url] mx pharmacy easy mx pharmacy easy mx pharmacy easy

mx pharmacy easy https://mxpharmacyeasy.shop/# mx pharmacy easy mx pharmacy easy

[url=https://mxpharmacyeasy.shop/#]mx pharmacy easy[/url] mx pharmacy easy mx pharmacy easy mx pharmacy easy

Emcd Io: надежная криптовалютная биржа или скам, отзывы инвесторов, можно ли вывести деньги из ЛК Emcd io Pool

[url=https://torforex.com/mayning-telegram/emcd-io-otzyvy/]emcd пул для майнинга отзывы[/url]

Владельцы проекта Emcd Io отзывы строго отслеживают, стараясь забивать любой негатив массивом положительных комментариев. И это нехороший звоночек, позволяющий усомниться в честности майнинг-биржи, надежности криптовалютного кошелька, безопасности P2P-переводов. Эта проверка расскажет, можно ли заработать на услугах “ЕМЦД ИО”, или это очередной лохотрон, созданный для выманивания денег с честных инвесторов?

пул emcd отзывы

https://torforex.com/mayning-telegram/emcd-io-otzyvy/

Что такое Emcd Io?

emcd io отзывы

[url=https://torforex.com/mayning-telegram/emcd-io-otzyvy/]emcd io отзывы[/url]

Gate Emcd Io – криптовалютный проект, созданный на базе крупнейшего майнинг-пула в Восточной Европе. Именно так позиционируют платформу ее создатели. Основное направление деятельности – передача асиков в аренду для добычи популярных монет, например, Bitcoin, Ethereum и других. Также компания предлагает сервис p2p-переводов и кошелек для хранения намайненных активов.

emcd io pool

Если верить официальному сайту Emcd Io, у компании более 300 тыс. клиентов, ежедневно выполняется более 2,7 млн транзакций. Но эта статистика не подтверждается финансовыми отчетами, которые обычно публикуют крупные компании с хорошей деловой репутацией.

emcd биржа отзывы

Контора заявляет, что работает честно и прозрачно, но тщательно скрывает юридическую информацию. Ее можно найти исключительно в тексте оферты. Платформа Emcd Io работает от имени двух компаний. EMCD Tech Limited зарегистрирована в Гонконге, отвечает за работу криптовалютной майнинг-фермы. Сервис пассивного дохода и криптокошелек действуют на базе лицензии Сейшельских островов, выданной компании EMCD Struct LTD.

mx pharmacy fast https://mxpharmacyfast.shop/# mx pharmacy fast mx pharmacy fast

Aerodrome Finance: Innovations and Opportunities

In today’s evolving landscape, the development of aerodrome infrastructure and related financial tools is becoming increasingly significant. This article explores key aspects of aerodrome finance, along with emerging trends in decentralized finance (DeFi), such as aerodrome swap, aerodrome exchange, and aerodrome DEX.

[url=https://aerfili.com/]aerodrome finance base[/url]

What is Aerodrome Finance?

Aerodrome finance refers to the integration of traditional aerodrome operations with modern financial technologies, enabling optimized management of assets, investments, and operations at aerodrome bases. This concept involves creating specialized aerodrome bases that serve as platforms for financial transactions and investment activities.

Aerodrome Base

An aerodrome base is a foundational platform that combines aerodrome infrastructure with financial instruments. It provides transparency, security, and efficiency in asset management and acts as a core for implementing innovative financial solutions.

Aerodrome Swap

An aerodrome swap is a financial instrument allowing participants to exchange assets or liabilities related to aerodrome infrastructure. Such swaps help manage risks associated with fluctuations in asset values or currency exchange rates.

Aerodrome Exchange

An aerodrome exchange is a marketplace for trading assets linked to aerodromes, including tokens representing infrastructure or other financial instruments. It ensures liquidity and market access for investors and operators.

Aerodrome DeFi Solutions

Aerodrome DeFi involves applying decentralized finance protocols within the aerodrome sector. This includes establishing aerodrome finance bases where users can obtain loans, participate in liquidity pools, and earn yields by providing liquidity.

Aerodrome DEX

An aerodrome DEX is a decentralized exchange that facilitates token swaps without intermediaries. This aerodrome DEX promotes local market development and enhances access to financial services for industry participants.

Aerodrome Finance: Innovations and Opportunities

In today’s evolving landscape, the development of aerodrome infrastructure and related financial tools is becoming increasingly significant. This article explores key aspects of aerodrome finance, along with emerging trends in decentralized finance (DeFi), such as aerodrome swap, aerodrome exchange, and aerodrome DEX.

[url=https://aerfili.com/]aerodrome dex[/url]

What is Aerodrome Finance?

Aerodrome finance refers to the integration of traditional aerodrome operations with modern financial technologies, enabling optimized management of assets, investments, and operations at aerodrome bases. This concept involves creating specialized aerodrome bases that serve as platforms for financial transactions and investment activities.

Aerodrome Base

An aerodrome base is a foundational platform that combines aerodrome infrastructure with financial instruments. It provides transparency, security, and efficiency in asset management and acts as a core for implementing innovative financial solutions.

Aerodrome Swap

An aerodrome swap is a financial instrument allowing participants to exchange assets or liabilities related to aerodrome infrastructure. Such swaps help manage risks associated with fluctuations in asset values or currency exchange rates.

Aerodrome Exchange

An aerodrome exchange is a marketplace for trading assets linked to aerodromes, including tokens representing infrastructure or other financial instruments. It ensures liquidity and market access for investors and operators.

Aerodrome DeFi Solutions

Aerodrome DeFi involves applying decentralized finance protocols within the aerodrome sector. This includes establishing aerodrome finance bases where users can obtain loans, participate in liquidity pools, and earn yields by providing liquidity.

Aerodrome DEX

An aerodrome DEX is a decentralized exchange that facilitates token swaps without intermediaries. This aerodrome DEX promotes local market development and enhances access to financial services for industry participants.

Aerodrome Finance: Innovations and Opportunities

In today’s evolving landscape, the development of aerodrome infrastructure and related financial tools is becoming increasingly significant. This article explores key aspects of aerodrome finance, along with emerging trends in decentralized finance (DeFi), such as aerodrome swap, aerodrome exchange, and aerodrome DEX.

[url=https://aerfili.com/]aerodrome dex[/url]

What is Aerodrome Finance?

Aerodrome finance refers to the integration of traditional aerodrome operations with modern financial technologies, enabling optimized management of assets, investments, and operations at aerodrome bases. This concept involves creating specialized aerodrome bases that serve as platforms for financial transactions and investment activities.

Aerodrome Base

An aerodrome base is a foundational platform that combines aerodrome infrastructure with financial instruments. It provides transparency, security, and efficiency in asset management and acts as a core for implementing innovative financial solutions.

Aerodrome Swap

An aerodrome swap is a financial instrument allowing participants to exchange assets or liabilities related to aerodrome infrastructure. Such swaps help manage risks associated with fluctuations in asset values or currency exchange rates.

Aerodrome Exchange

An aerodrome exchange is a marketplace for trading assets linked to aerodromes, including tokens representing infrastructure or other financial instruments. It ensures liquidity and market access for investors and operators.

Aerodrome DeFi Solutions

Aerodrome DeFi involves applying decentralized finance protocols within the aerodrome sector. This includes establishing aerodrome finance bases where users can obtain loans, participate in liquidity pools, and earn yields by providing liquidity.

Aerodrome DEX

An aerodrome DEX is a decentralized exchange that facilitates token swaps without intermediaries. This aerodrome DEX promotes local market development and enhances access to financial services for industry participants.

[url=https://mxpharmacyfast.shop/#]mx pharmacy fast[/url] mx pharmacy fast mx pharmacy fast mx pharmacy fast

Ethena: The Future of Crypto and DeFi Innovation

Ethena is rapidly emerging as a prominent name in the world of cryptocurrency and decentralized finance (DeFi). With a focus on security, innovation, and user-centric solutions, Ethena is shaping the future of digital assets and financial protocols. Let’s explore the key aspects associated with Ethena, including its platforms, tokens, and ecosystem.

[url=https://etenfili.com/]ethena lab[/url]

Ethena Overview

Ethena is a blockchain project dedicated to creating secure, scalable, and user-friendly DeFi solutions. Its ecosystem encompasses various components such as Ethena Fi, Ethena Lab, and its native tokens like Ethena USDE. The project aims to bridge traditional finance with innovative crypto solutions, making decentralized finance accessible to a broader audience.

Ethena Fi

Ethena Fi is the decentralized finance platform built on the Ethena ecosystem. It offers a suite of financial products including lending, borrowing, staking, and yield farming. Ethena Fi emphasizes security and transparency, providing users with reliable tools to grow their crypto assets.

Ethena Finance

Ethena Finance refers to the broader financial ecosystem powered by Ethena’s blockchain technology. It integrates various DeFi protocols, enabling seamless asset management, liquidity provision, and crypto trading. Ethena Finance aims to create a comprehensive financial environment where users can leverage their crypto holdings efficiently.

Ethena Lab

Ethena Lab is the innovation hub within the Ethena ecosystem. It focuses on research, development, and testing of new blockchain solutions, smart contracts, and DeFi protocols. Ethena Lab drives continuous innovation, ensuring the platform remains at the forefront of crypto technology.

Ethena USDE

Ethena USDE is the native stablecoin of the Ethena ecosystem. Pegged to a stable asset, USDE provides a reliable medium of exchange within the platform, facilitating smooth transactions, lending, and borrowing activities. It aims to maintain stability while offering the benefits of decentralization.

Ethena Finance Crypto

Ethena Finance crypto encompasses the entire range of digital assets, tokens, and protocols developed under the Ethena project. It includes the native tokens, stablecoins, and other crypto assets that facilitate DeFi operations, liquidity pools, and decentralized trading.

Ethena: The Future of Crypto and DeFi Innovation

Ethena is rapidly emerging as a prominent name in the world of cryptocurrency and decentralized finance (DeFi). With a focus on security, innovation, and user-centric solutions, Ethena is shaping the future of digital assets and financial protocols. Let’s explore the key aspects associated with Ethena, including its platforms, tokens, and ecosystem.

[url=https://etenfili.com/]ethena lab[/url]

Ethena Overview

Ethena is a blockchain project dedicated to creating secure, scalable, and user-friendly DeFi solutions. Its ecosystem encompasses various components such as Ethena Fi, Ethena Lab, and its native tokens like Ethena USDE. The project aims to bridge traditional finance with innovative crypto solutions, making decentralized finance accessible to a broader audience.

Ethena Fi

Ethena Fi is the decentralized finance platform built on the Ethena ecosystem. It offers a suite of financial products including lending, borrowing, staking, and yield farming. Ethena Fi emphasizes security and transparency, providing users with reliable tools to grow their crypto assets.

Ethena Finance

Ethena Finance refers to the broader financial ecosystem powered by Ethena’s blockchain technology. It integrates various DeFi protocols, enabling seamless asset management, liquidity provision, and crypto trading. Ethena Finance aims to create a comprehensive financial environment where users can leverage their crypto holdings efficiently.

Ethena Lab

Ethena Lab is the innovation hub within the Ethena ecosystem. It focuses on research, development, and testing of new blockchain solutions, smart contracts, and DeFi protocols. Ethena Lab drives continuous innovation, ensuring the platform remains at the forefront of crypto technology.

Ethena USDE

Ethena USDE is the native stablecoin of the Ethena ecosystem. Pegged to a stable asset, USDE provides a reliable medium of exchange within the platform, facilitating smooth transactions, lending, and borrowing activities. It aims to maintain stability while offering the benefits of decentralization.

Ethena Finance Crypto

Ethena Finance crypto encompasses the entire range of digital assets, tokens, and protocols developed under the Ethena project. It includes the native tokens, stablecoins, and other crypto assets that facilitate DeFi operations, liquidity pools, and decentralized trading.

mx pharmacy fast https://mxpharmacyfast.shop/# mx pharmacy fast mx pharmacy fast

[url=https://mxpharmacyfast.shop/#]mx pharmacy fast[/url] mx pharmacy fast mx pharmacy fast mx pharmacy fast

mx pharmacy fast https://mxpharmacyfast.shop/# mx pharmacy fast mx pharmacy fast

[url=https://mxpharmacyfast.shop/#]mx pharmacy fast[/url] mx pharmacy fast mx pharmacy fast mx pharmacy fast

mx pharmacy fast https://mxpharmacyfast.shop/# mx pharmacy fast mx pharmacy fast

[url=https://chimmed.ru/products/4-imidazolidinone-95-id=4680927]4 imidazolidinone 95% – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]6 fluoropyridin 2 yl methanamine min. 95% – купить онлайн в интернет-магазине химмед [/u]

[i]6 fluoropyridin 3 yl hydrazine 95% – купить онлайн в интернет-магазине химмед [/i]

[b]6 fluoropyridin 3 yl methanamine – купить онлайн в интернет-магазине химмед [/b]

4 imidazolecarboxaldehyde pure, 98% – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/4-imidazolkarbonovyy-aldegid-chistyy-98-id=6262627

[url=https://mxpharmacyfast.shop/#]mx pharmacy fast[/url] mx pharmacy fast mx pharmacy fast mx pharmacy fast

[url=https://chimmed.ru/products/kromasil-60-16-sil-column-id=273068]kromasil 60 16 sil column – купить онлайн в интернет-магазине химмед [/url]

Tegs: [u]nucleosil 100 10c18 150 x 4.6mm – купить онлайн в интернет-магазине химмед [/u]

[i]nucleosil 100 10c18 200×4.0mm – купить онлайн в интернет-магазине химмед [/i]

[b]nucleosil 100 10c18 250 x 4.0mm – купить онлайн в интернет-магазине химмед [/b]

kromasil 60 16 sil column – купить онлайн в интернет-магазине химмед https://chimmed.ru/products/kromasil-60-16-sil-column-id=273069

mx pharmacy fast https://mxpharmacyfast.shop/# mx pharmacy fast mx pharmacy fast

[url=https://mxpharmacyfast.shop/#]mx pharmacy fast[/url] mx pharmacy fast mx pharmacy fast mx pharmacy fast

phar modafinil https://pharmodafinil.shop/# phar modafinil phar modafinil

[url=https://pharmodafinil.shop/#]phar modafinil[/url] phar modafinil phar modafinil phar modafinil

phar modafinil https://pharmodafinil.shop/# phar modafinil phar modafinil

‘Like wildfires underwater’: Worst summer on record for Great Barrier Reef as coral die-off sweeps planet

[url=https://tripscan.biz]трип скан[/url]

Great Barrier Reef, Australia

CNN

—

As the early-morning sun rises over the Great Barrier Reef, its light pierces the turquoise waters of a shallow lagoon, bringing more than a dozen turtles to life.

These waters that surround Lady Elliot Island, off the eastern coast of Australia, provide some of the most spectacular snorkeling in the world — but they are also on the front line of the climate crisis, as one of the first places to suffer a mass coral bleaching event that has now spread across the world.

https://tripscan.biz

tripskan

The Great Barrier Reef just experienced its worst summer on record, and the US-based National Oceanic and Atmospheric Administration (NOAA) announced last month that the world is undergoing a rare global mass coral bleaching event — the fourth since the late 1990s — impacting at least 53 countries.

The corals are casualties of surging global temperatures which have smashed historical records in the past year — caused mainly by fossil fuels driving up carbon emissions and accelerated by the El Nino weather pattern, which heats ocean temperatures in this part of the world.

CNN witnessed bleaching on the Great Barrier Reef in mid-February, on five different reefs spanning the northern and southern parts of the 2,300-kilometer (1,400-mile) ecosystem.

“What is happening now in our oceans is like wildfires underwater,” said Kate Quigley, principal research scientist at Australia’s Minderoo Foundation. “We’re going to have so much warming that we’re going to get to a tipping point, and we won’t be able to come back from that.”

Coral bleached white from high water temperatures on the Great Barrier Reef, Australia. CNN

Bleaching occurs when marine heatwaves put corals under stress, causing them to expel algae from their tissue, draining their color. Corals can recover from bleaching if the temperatures return to normal, but they will perish if the water stays warmer than usual.

“It’s a die-off,” said Professor Ove Hoegh-Guldberg, a climate scientist at the University of Queensland in Australia and chief scientist at The Great Barrier Reef Foundation. “The temperatures got so warm, they’re off the charts … they never occurred before at this sort of level.”

The destruction of marine ecosystems would deliver an effective death sentence for around a quarter of all species that depend on reefs for survival — and threaten an estimated billion people who rely on reef fish for their food and livelihoods. Reefs also provide vital protection for coastlines, reducing the impact of floods, cyclones and sea level rise.

“Humanity is being threatened at a rate by which I’m not sure we really understand,” Hoegh-Guldberg said.

President Donald Trump speaks about the mid-air crash between American Airlines flight 5342 and a military helicopter in Washington. Roberto Schmidt/AFP/Getty Images

New York

CNN

— [url=https://https-blacksprut.ru]блэкспрут[/url]

President Donald Trump on Thursday blamed the Federal Aviation Administration’s “diversity push” in part for the plane collision that killed 67 people in Washington, DC. But DEI backers, including most top US companies, believe a push for diversity has been good for their businesses.

Trump did not cite any evidence for how efforts to hire more minorities, people with disabilities and other groups less represented in American workforces led to the crash, saying “it just could have been” and that he had “common sense.” But Trump criticized the FAA’s effort to recruit people with disabilities during Joe Biden’s administration, even though the FAA’s Aviation Safety Workforce Plan for the 2020-2029 period, issued under Trump’s first administration, promoted and supported “the hiring of people with disabilities and targeted disabilities.”

[url=https://tor-blacksprut.ru]blacksprut[/url]

It’s not the first time opponents of diversity, equity and inclusion initiatives, or DEI, have said they can kill people. “DEI means people DIE,” Elon Musk said after the California wildfires, criticizing the Los Angeles Fire Department and city and state officials for their efforts to advance diversity in their workforces.

blacksprut ссылка

https://bs-gl.cc

[url=https://pharmodafinil.shop/#]phar modafinil[/url] phar modafinil phar modafinil phar modafinil

phar modafinil https://pharmodafinil.shop/# phar modafinil phar modafinil

[url=https://pharmodafinil.shop/#]phar modafinil[/url] phar modafinil phar modafinil phar modafinil

Ролик создан, грузит без проблем https://rutube.ru/video/220f5082b659620c25a8577d96926b4d/?r=wd

phar modafinil https://pharmodafinil.shop/# phar modafinil phar modafinil

Тесты синергии и их роль в современном образовании и бизнесе

В современном мире концепция синергии становится все более актуальной как в сфере образования, так и в бизнесе. Термин «синергия» обозначает эффект, при котором сумма результатов совместных действий превышает сумму результатов отдельных участников.

[url=https://xn—-ftbeboc6azaebhc1juc.xn--p1ai/]Тесты Синергии[/url]

В контексте образовательных программ и производственной практики, тесты синергии служат инструментом оценки эффективности взаимодействия студентов, преподавателей и предприятий, а также помогают выявить потенциал для дальнейшего развития.

https://xn—-ftbeboc6azaebhc1juc.xn--p1ai/

Практика Синергии

Практика синергии — это неотъемлемая часть подготовки специалистов, которая позволяет студентам применить полученные знания на практике, развить командные навыки и понять реальные требования рынка труда. В рамках производственной практики синергия достигается через совместную работу студентов с предприятиями, что способствует обмену опытом, развитию профессиональных компетенций и формированию командного духа. Такой подход помогает студентам не только закрепить теоретические знания, но и научиться решать реальные задачи, что значительно повышает их конкурентоспособность на рынке труда.

Практика синергии в рамках университетов, таких как Университет «Синергия», включает в себя разнообразные программы, направленные на развитие междисциплинарных навыков и создание условий для эффективного взаимодействия между студентами и работодателями. Университет «Синергия» активно внедряет современные методы обучения, в том числе проектную деятельность, стажировки и корпоративные проекты, что способствует формированию у студентов системного мышления и умения работать в команде.

Купить практику синергия — это возможность для компаний и студентов получить доступ к качественной образовательной и производственной базе, а также к экспертам и наставникам, которые помогают реализовать проекты любой сложности. Для студентов это шанс получить уникальный опыт, повысить свою профессиональную ценность и подготовиться к реальным условиям работы. Для работодателей — возможность найти талантливых специалистов, которые уже прошли проверку на практике и готовы к выполнению сложных задач.

Образовательные учреждения, такие как университет «Синергия», предлагают разнообразные программы практики, которые позволяют студентам не только приобрести практический опыт, но и развить навыки коммуникации, лидерства и управления проектами. В результате, такие практики способствуют формированию профессиональной среды, где ценится командная работа, инновации и постоянное развитие.

В целом, тесты синергии и практика синергии являются важными инструментами для повышения качества образования и эффективности бизнес-процессов. Они помогают выявить сильные стороны участников, определить зоны для улучшения и создать условия для достижения максимальных результатов. В современном мире, где конкуренция растет с каждым годом, умение работать в команде и использовать синергетический эффект становится ключевым фактором успеха как для отдельных специалистов, так и для организаций в целом.

[url=https://buyedpills.shop/#]edmeds buy[/url] edpills buy edpills buy edpills buy

Этот информативный текст отличается привлекательным содержанием и актуальными данными. Мы предлагаем читателям взглянуть на привычные вещи под новым углом, предоставляя интересный и доступный материал. Получите удовольствие от чтения и расширьте кругозор!

Разобраться лучше – https://vyvod-iz-zapoya-1.ru/

edmeds buy https://buyedpills.shop/# edmeds buy edpills buy

[url=https://buyedpills.shop/#]edpills buy[/url] edmeds buy edmeds buy edpills buy

Наклоняемые платформы.

TF30 NOBLELIFT Подъемный стол гидравлический.

Арт. 700143.

Высота подъёма: 1100 мм.

Грузоподъемность: 1500 кг.

Грузоподъемность: 500 кг.

edmeds buy https://buyedmeds.shop/# edmeds buy edpills buy

[b]Name novel[/b] capsules for enormous climaxes – more also greater strong culminations!

[b]by observed[/b] before – greatly newest of therapeutic research exploration!

[b]Completely risk-free[/b] also potent – likewise enhanced lust well yet raised penile firmness!

[url=https://psee.io/7qlgd7][b]Boost quantity in own discharges now right now![/b][/url]

[url=https://buyedpills.shop/#]edpills buy[/url] edpills buy edmeds buy edmeds buy

edmeds buy https://buyedmeds.shop/# edmeds buy edmeds buy

[url=https://buyedpills.shop/#]edpills buy[/url] edmeds buy edpills buy edpills buy

edmeds buy https://buyedpills.shop/# edmeds buy edpills buy

Привет всем. Решил написать свой небольшой опыт работы с Kraken, возможно, кому-то пригодится. Использую этот маркетплейс уже достаточно давно, и хочу сразу отметить, что заходить на него без TOR-браузера смысла нет, так как это даркнет-площадка. Официальный сайт Kraken доступен только через TOR, и из всех ссылок, которые я проверял за последние месяцы, самой стабильной для меня оказалась krakr.cc |

⠀

Раньше я пользовался другими зеркалами Kraken, но часто возникали проблемы – то сайт не грузится, то появляется ошибка подключения, то onion-ссылка оказывается неактивной. Особенно это напрягало, когда нужно было срочно проверить баланс или статус заказа. krakr.cc работает без перебоев, грузится быстро и самое главное – всегда актуален.

⠀

Для тех, кто не знает, Kraken – это крупнейший маркетплейс в даркнете, где продаются разные товары, но я использую его исключительно как пример безопасности работы через TOR и в целях тестирования SEO-переходов для своих проектов. Многие пишут, что Kraken небезопасен, но на самом деле все зависит от того, какую ссылку вы используете и насколько правильно настраиваете TOR. Например, при входе через krakr.cc проблем с безопасностью не было, так как сайт открывается напрямую через onion-ссылку без лишних редиректов.

⠀

Также хочу сказать, что перед тем как заходить на Kraken, всегда обновляйте TOR-браузер до последней версии. Это важно, так как многие зеркала могут быть недоступны из-за устаревшей версии браузера. Второй момент – отключайте любые плагины и VPN, если используете TOR. Он и так работает через цепочку прокси, а сторонние VPN могут только замедлить загрузку.

⠀

На krakr.cc вход максимально простой: заходите через TOR, появляется форма авторизации, вводите свои данные и сразу попадаете на маркетплейс. Никаких дополнительных проверок с капчами, как на других зеркалах Kraken, здесь нет. Сайт грузится буквально за 2-3 секунды, при стабильном соединении даже быстрее.

⠀

Теперь немного про комиссии Kraken. Многие спрашивают, какие проценты берет площадка. Все зависит от категории товара, но в среднем комиссия Kraken составляет от 2% до 5%, если речь идет о цифровых товарах, например, программах, курсах, аккаунтах и т.д. Если брать физические товары, комиссия может доходить до 8-10%. Однако, учитывая безопасность сделок и встроенный эскроу, эти проценты вполне оправданы.

⠀

Что касается отзывов, то лично я никогда не сталкивался с обманом на Kraken, если брать у продавцов с высоким рейтингом. Конечно, всегда есть риск, особенно если покупаете у новичков без отзывов, но это правило работает на всех маркетплейсах, не только в даркнете.

⠀